Electrostatic discharge (ESD) remains one of the most pervasive threats to modern electronics, with transient voltages exceeding 15kV capable of destroying components in nanoseconds. Effective ESD protection requires a hierarchical approach addressing three critical levels: component selection, circuit design, and system integration.

Component-Level Solutions

The first line of defense involves strategic component selection. Transient voltage suppression (TVS) diodes dominate high-performance applications, offering response times under 1 nanosecond and power handling up to 5kW. For cost-sensitive designs, multilayer varistors (MLVs) provide adequate protection at 1/3 the cost. Advanced ICs now integrate silicon-controlled rectifier (SCR) structures directly into chips, with holding voltages below 5V and current capacity exceeding 10A. These components work by creating controlled discharge paths when voltages exceed safe thresholds.

Circuit Design Techniques

Effective PCB implementation requires three key elements: power rail clamps, signal path protection, and intelligent layout. Rail clamps using large MOSFETs or diode strings must activate within 5ns to prevent latch-up. Every I/O pin needs dedicated protection cells sized according to expected stress levels – typically 2kV HBM for consumer devices, 8kV for industrial. The 3W layout rule (trace spacing = 3×width) minimizes coupling, while guard rings around sensitive analog circuits reduce noise coupling by 15-20dB.

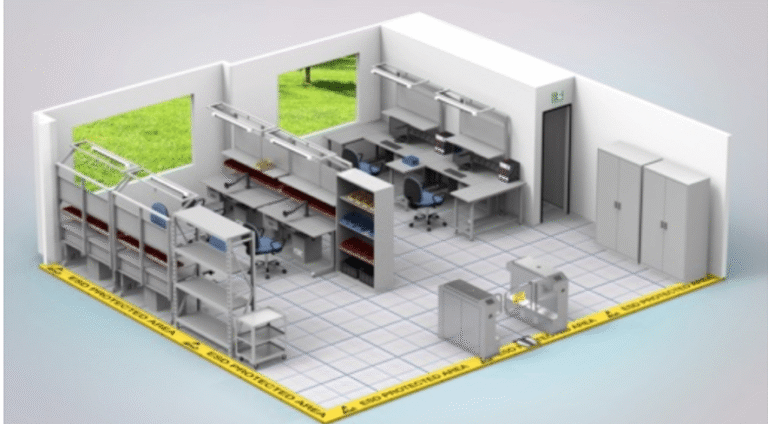

System Integration

Robust systems employ four key strategies:

1. Star-point grounding with impedance below 0.5Ω

2. Conductive enclosures providing 60dB attenuation at 1GHz

3. Interface protection meeting IEC 61000-4-2 Level 4 (±8kV contact/±15kV air)

4. Proper handling procedures including 1MΩ wrist straps and dissipative work surfaces

Implementation Examples

1. USB 3.0 ports typically use 3.3V TVS arrays with 0.5pF capacitance

2. Automotive ECUs combine ISO7637-2 compliant protection with 8-layer PCBs

3. Industrial controls require 8kV IEC protection plus environmental sealing

Design Tradeoffs

Engineers must balance:

– Protection level vs signal integrity (capacitance <0.5pF for HDMI 2.1)

– Component size vs performance (0402 packages limit power handling)

– Cost vs reliability ($0.10 protection for $1 IC vs $1 protection for $100 IC)

Standards Compliance

Modern designs must meet:

– Component-level: JESD22-A114 (HBM), A115 (CDM)

– System-level: IEC 61000-4-2 Level 4

– Automotive: ISO10605 (up to 25kV)

Future Challenges

5G devices require protection up to 28GHz, while IoT nodes need sub-$0.05 solutions. Emerging materials like graphene may enable 0.1pF TVS devices by 2025.

Effective ESD protection requires understanding discharge mechanisms, component characteristics, and system interactions. As electronics shrink, protection must evolve – the industry is moving toward integrated solutions combining TVS, filters, and EMI shielding in single packages. Designers must stay current with both component advances and evolving standards.